Description

10Mbps, Enhanced Bit Rate 1553 IP Core for FPGA and ASIC, Development License, Including 10 Prototype Units

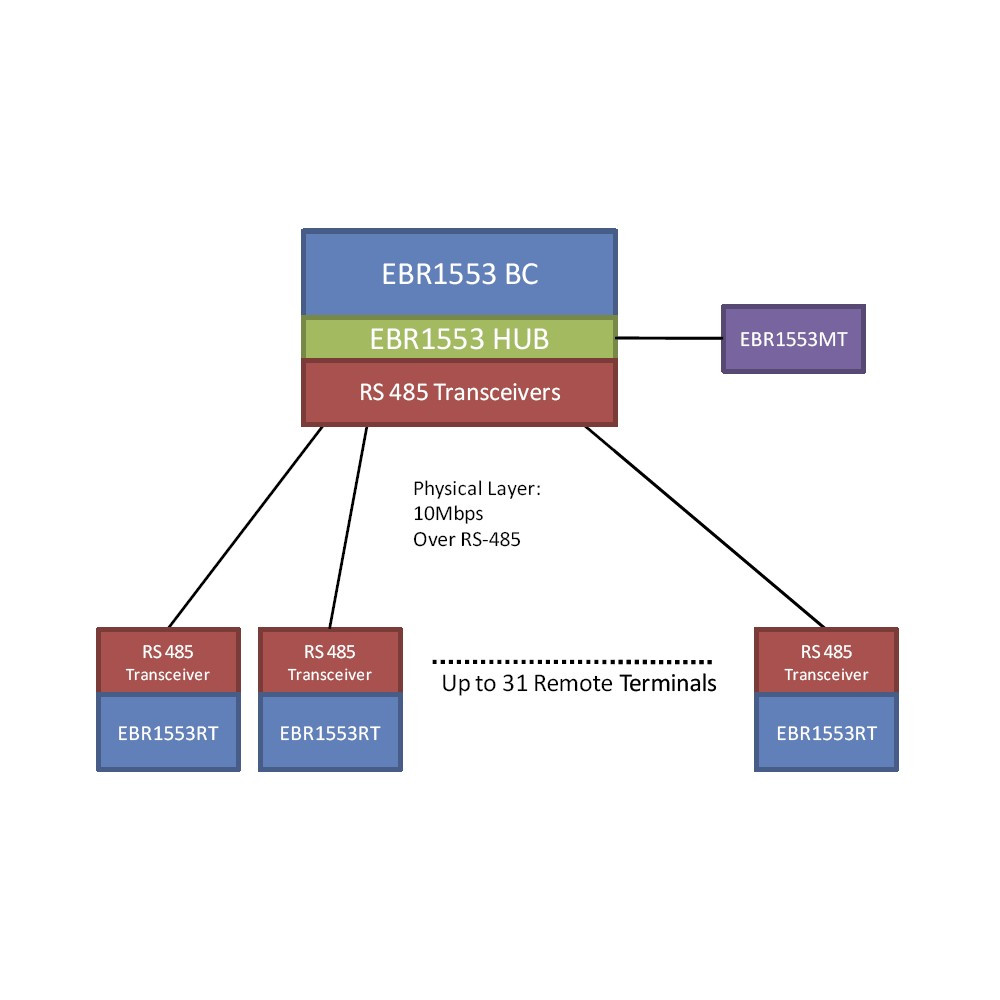

The EBR-1553 uses MIL-STD-1553 protocol to provide a 10Mbps bit rate protocol over RS-485 transceivers in a hub-based point-to-point connection. Using network topology of a star between BC and Remote Terminals enables high-speed and robust data transfer.

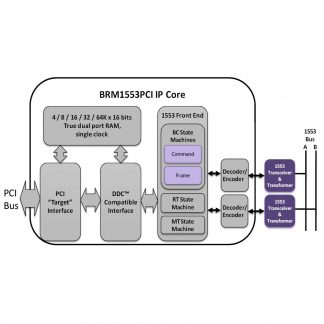

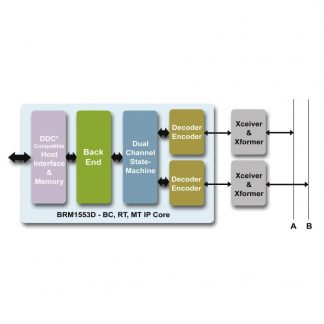

The EBR-1553 IP core is DDC® Enhanced Mini-ACE® compatible, and Bus Controller, Remote Terminals and Bus Monitor IP core configurations are available. The core can work with any FPGA, requires only standard RS-485 transceivers, and supports 10Mbps.

BC Mode and its HUB

In EBR1553 the BC manages a HUB for star topology. This HUB is built of up to 31 RS-485 transceivers, each having a single Tx and Rx line. The decoder and encoders inside the EBR1553D core were upgraded to handle this single line bus, and assumes that the transceivers are biased to ‘1’. This means that when no one transmits on the bus, the Rx line would read ‘1’. Modern RS-485 transceivers are internally biased, thus the biasing resistors can be avoided.

The width of the HUB is a synthesis parameter that needs to be provided prior to the supply of the IP core.

The BRM1553D-EBR IP core also supports a RS-485 multi-drop configuration.

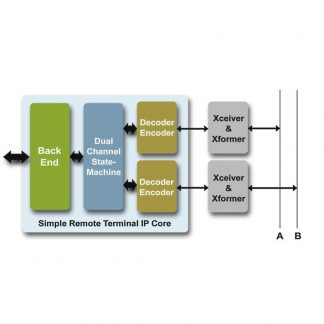

RT Mode

In RT mode, the IP core is connected to a single RS-485 transceiver, which is connected to one of the ports of the BC. The RT address can be set by software or by hardware pins. All mode codes are supported, as well as illegalization of mode codes and commands.

MT Mode

In MT mode, there is no transmission, only bus monitoring. In this case the HUB Width is set to 1. The MT might also connect to a wider HUB (i.e., to multiple HUB stubs), but it can only record a single RT response (as EBR1553 defined).

RT / MON Mode

The BRM1553D EBR can function as an RT/MON as in regular MIL-STD-1553. This is a software selectable mode.

Back End Interface

Includes DDC® Enhanced Mini-ACE® interface, compatible with existing drivers and applications.

- No need to rewrite drivers’ code

- Eliminates replacement risk

Manchester Decoder

The unique Manchester decoder can work with any clock frequency from 120MHz and up to reduce clock sources and clock domains onboard (reduces EMI/RFI) and ease the integration with back-end interface. Advanced algorithms for filtering out noise and disturbances enable the core to operate in harsh environments.

* DDC® and Mini-ACE® are registered trademarks of Data Device Corporation, Bohemia, NY, USA. There is no affiliation between Data Device Corporation and Sital Technology, Ltd or Sealevel Systems Inc. Sealevel is the licensed partner of Sital Technologies, Kfar-Saba, Israel, for distribution in the United States of Sital MIL-STD-1553 products and IP core products.

Reviews

There are no reviews yet.