Description

MIL-STD-1553B Notice 2 Remote Terminal, Bus Controller, Monitor Front End Core for FPGA and ASIC Devices, Development License, Including 10 Prototype Units

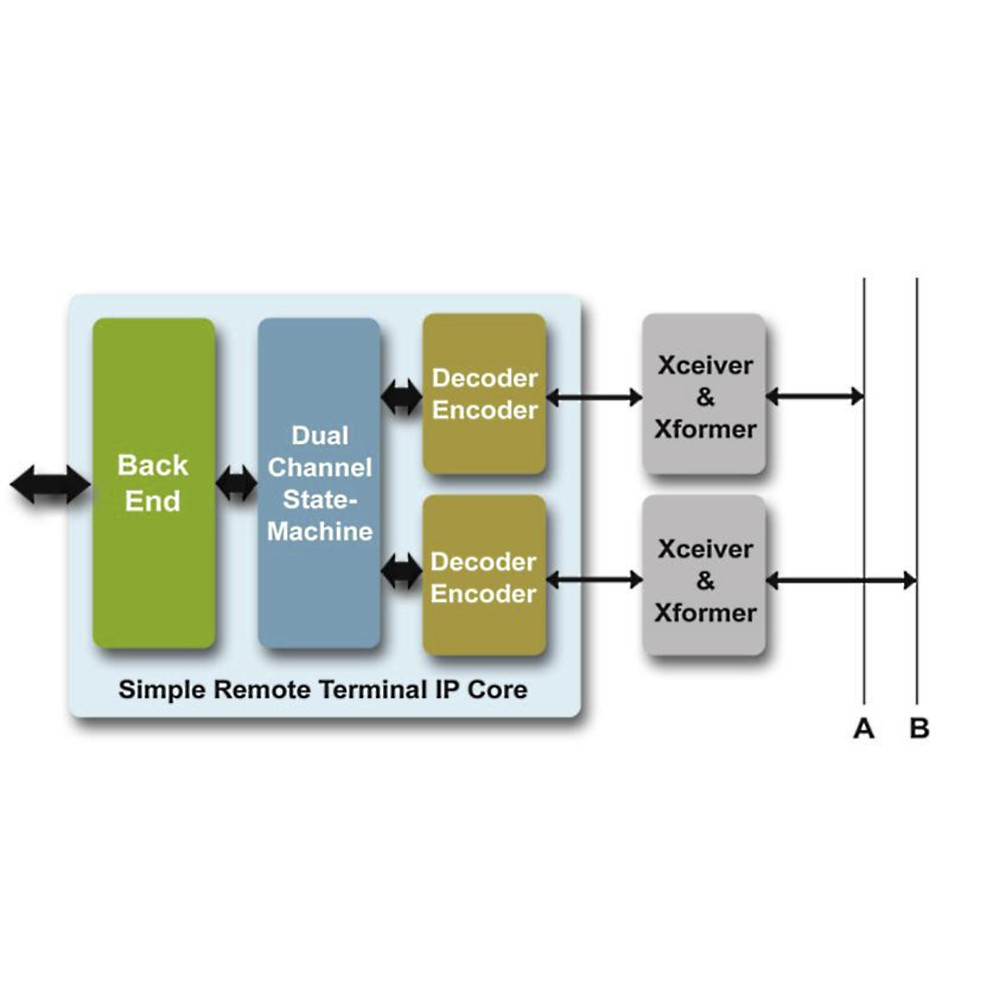

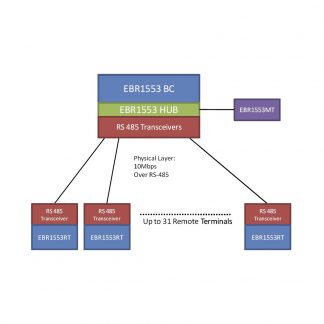

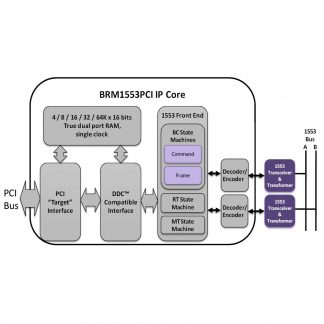

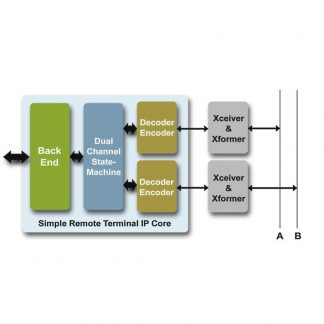

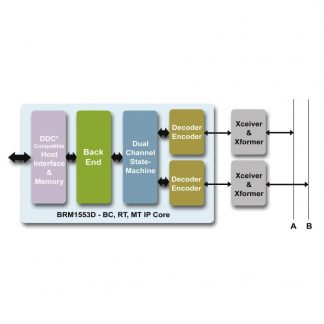

Designed for applications that require relatively short messages, the BC/RT/MT 1553FE IP core enables MIL-STD-1553 functionality using a standard FPGA. The core is particularly useful in obsolete replacement designs and simple applications.

Back End Interface

The BC/RT/MT 1553FE interfaces with the back-end through simple address-data read and write “bus cycles”.

- No CPU is required

- Simple integration with user’s logic

Gate Count

A small gate count is required from an FPGA device even for complex applications, minimizing cost and the space required on the target board.

Manchester Decoder

The unique Manchester decoder can work with any clock frequency from 12Mhz and up to reduce clock sources and clock domains onboard (reduces EMI/RFI). Advanced algorithms for filtering out noise and disturbances enable the core to operate in harsh environments.

Transceivers

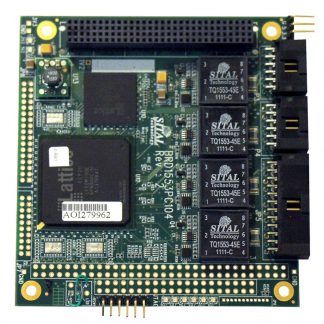

The BRM1553FE IP core connects to any standard transceiver-transformer pair. The core was fully validated with a 3rd party dual transceiver.

RT Validation

The BRM1553FE IP core has been successfully implemented in a 3rd party FPGA, and has passed the full MIL-STD-1553B Notice 2 RT Validation test plan in an independent laboratory.

* Sealevel is the licensed partner of Sital Technologies, Kfar-Saba, Israel, for distribution in the United States of Sital MIL-STD-1553 products and IP core products.

Reviews

There are no reviews yet.