Overview

Connecting modern computer equipment to proprietary, often old, infrastructure is a common requirement in military applications. For example, Sealevel was contacted by the manufacturer of a rugged, military computer server to design an interface to radio modems installed in aircraft. The radio modems use a proprietary, synchronous protocol as the host interface with little documentation available and no opportunity for modification. The computer server is designed to minimize size and power, so standard expansion slots for adding I/O are not available. However, there is a single PCI Express (PCIe) Mini Card slot available on the computer’s internal computer board that represents the only option for adding an I/O card.

Sealevel is an expert in synchronous communications and it is common that we assist customers with solutions for proprietary synchronous protocols. In this case, we were asked to design a PCIe Mini Card that interfaces via the internal expansion slot and supports the format of the radio modem’s communications.

Application Requirements

- Synchronous RS-423 interface

- High Frequency (HF) synchronous data stream

- Support for serial handshake signals

- Full-size PCIe Mini Card form factor

- Low emissions (EMI/EMC)

- Vibration tolerant

The Sealevel Solution

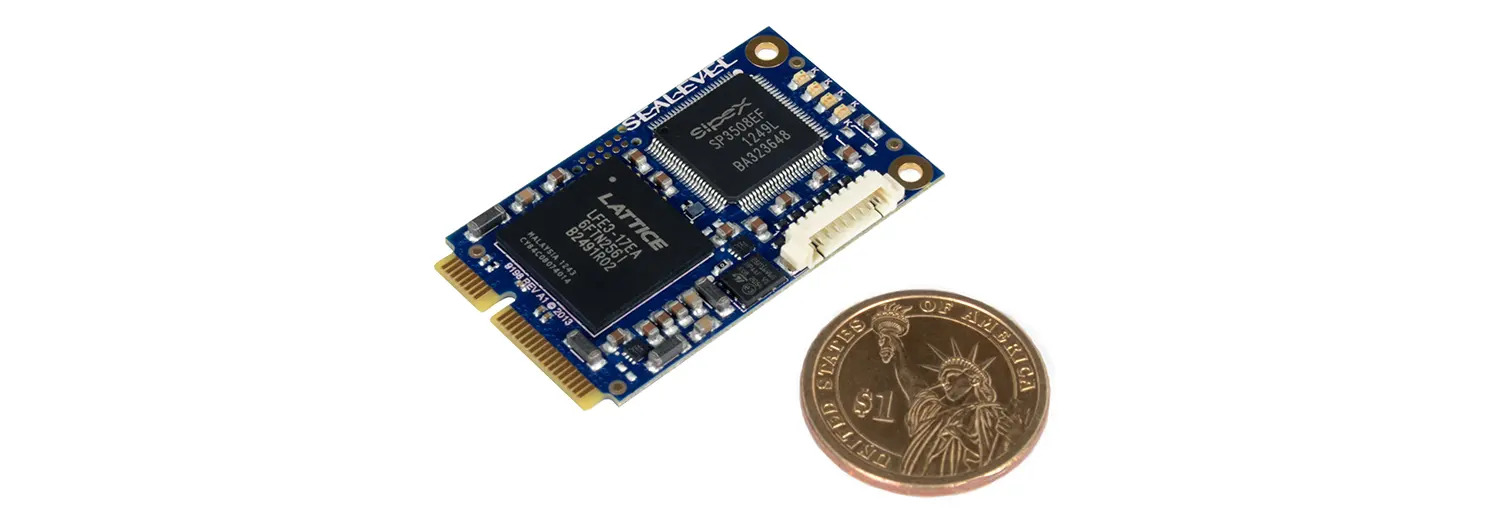

Sealevel designed a full-size PCIe Mini Card that met the maximum size envelope of 50.95 mm x 30.00 mm x 5.00 mm. The board provides a small, 9-pin Molex locking connector mounted to the board that accepts the mating cable which brings the communications signals to the exterior of the military computer.

Key Design Challenge

Small Footprint

Sealevel’s electrical team created an innovative, extremely small board that met the mechanical requirements while still providing the exact communication protocol required by the radio modem. Key to the implementation is the use of a Field Programmable Gate Array (FPGA).

The FPGA contains the PCI Express interface IP and the custom synchronous serial control logic. The FPGA is coupled with a multi-protocol transceiver to drive and receive the RS-423 signals and provides Transmit and Receive FIFOs that are custom-sized for the required protocol and data rates, but may be resized for other applications. The FPGA offloads the host processor by sensing the sync pattern and only interrupting the Sealevel-provided driver after a valid frame has been received. The FPGA also handles transmit of a host-configurable idle pattern when not transmitting data. The transmit and receive clocks are separate, and may run at different rates. The clock rates are measured by the FPGA and reported to the driver/host upon request. The Sealevel PCIe Sync Serial FPGA architecture is extensible and scalable to serve various custom synchronous serial protocols and applications. The sync serial control logic is architecture independent, and may be retargeted to other FPGA device families or vendors to guard against obsolescence.